Il set di istruzioni o l'architettura del set di istruzioni è la struttura del computer che fornisce comandi al computer per guidare il computer per l'elaborazione della manipolazione dei dati. Il set di istruzioni è costituito da istruzioni, modalità di indirizzamento, tipi di dati nativi, registri, interrupt, gestione delle eccezioni e architettura della memoria. Il set di istruzioni può essere emulato nel software utilizzando un interprete o integrato nell'hardware del processore. L'architettura del set di istruzioni può essere considerata come un confine tra il software e l'hardware. Classificazione dei microcontrollori e i microprocessori possono essere eseguiti sulla base dell'architettura del set di istruzioni RISC e CISC.

Set di istruzioni del processore

Il set di istruzioni specifica la funzionalità del processore comprese le operazioni supportate dal processore, i meccanismi di memorizzazione del processore e il modo di compilare i programmi nel processore.

Cosa sono RISC e CISC?

Il RISC e CISC può essere ampliato come segue:

RISC rappresenta il computer con set di istruzioni ridotto e

CISC rappresenta il Complex Instruction Set Computer.

Architettura RISC (Reduced Instruction Set Computer)

Architettura RISC

Il architettura del microcontrollore che utilizza un set di istruzioni piccolo e altamente ottimizzato è definito Computer con set di istruzioni ridotto o semplicemente RISC. Viene anche chiamata architettura LOAD / STORE.

Alla fine degli anni '70 e all'inizio degli anni '80, i progetti RISC furono sviluppati principalmente da Stanford, UC-Berkley e IBM. Il team di ricerca John Coke dell'IBM ha sviluppato RISC riducendo il numero di istruzioni necessarie per elaborare i calcoli più velocemente del CISC. L'architettura RISC è più veloce e i chip necessari per la produzione dell'architettura RISC sono anche meno costosi rispetto all'architettura CISC.

Caratteristiche tipiche dell'architettura RISC

- Tecnica di pipelining di RISC, esegue più parti o fasi di istruzioni contemporaneamente in modo tale che ogni istruzione sulla CPU sia ottimizzata. Quindi, i processori RISC hanno Clock per Instruction di un ciclo, e questo è chiamato come One Cycle Execution.

- Ottimizza il utilizzo del registro con un numero maggiore di registri nel RISC e un numero maggiore di interazioni all'interno della memoria può essere prevenuto.

- Semplici modalità di indirizzamento, anche complesse possono essere eseguite utilizzando l'aritmetica AND / OR operazioni logiche .

- Semplifica la progettazione del compilatore utilizzando registri generici identici che consentono di utilizzare qualsiasi registro in qualsiasi contesto.

- Per un utilizzo efficiente dei registri e l'ottimizzazione degli usi del pipelining, è necessario un set di istruzioni ridotto.

- Il numero di bit utilizzati per il codice operativo è ridotto.

- In generale ci sono 32 o più registri nel RISC.

Vantaggi dell'architettura del processore RISC

- A causa del piccolo insieme di istruzioni di RISC, i compilatori di linguaggio di alto livello possono produrre codice più efficiente.

- RISC consente la libertà di utilizzare lo spazio su microprocessori per la sua semplicità.

- Invece di utilizzare Stack, molti processori RISC utilizzano i registri per passare gli argomenti e contenere le variabili locali.

- Le funzioni RISC utilizzano solo pochi parametri ei processori RISC non possono utilizzare le istruzioni di chiamata e pertanto utilizzano istruzioni di lunghezza fissa che sono facili da pipeline.

- La velocità dell'operazione può essere massimizzata e il tempo di esecuzione può essere ridotto al minimo.

- Sono necessari un numero molto inferiore di formati di istruzione (meno di quattro), un numero limitato di istruzioni (circa 150) e alcune modalità di indirizzamento (meno di quattro).

Svantaggi dell'architettura del processore RISC

- Con l'aumento della lunghezza delle istruzioni, aumenta la complessità da eseguire per i processori RISC a causa del ciclo di caratteri per istruzione.

- Le prestazioni dei processori RISC dipendono principalmente dal compilatore o dal programmatore poiché la conoscenza del compilatore gioca un ruolo importante durante la conversione del codice CISC in un codice RISC, quindi la qualità del codice generato dipende dal compilatore.

- Durante la riprogrammazione del codice CISC in un codice RISC, definito come espansione del codice, le dimensioni aumenteranno. E la qualità di questa espansione del codice dipenderà ancora dal compilatore e anche dal set di istruzioni della macchina.

- La cache di primo livello dei processori RISC è anche uno svantaggio del RISC, in cui questi processori hanno grandi cache di memoria sul chip stesso. Per alimentare le istruzioni, richiedono molto sistemi di memoria veloci .

Architettura CISC (Complex Instruction Set Computer)

Lo scopo principale dell'architettura del processore CISC è completare l'attività utilizzando un numero inferiore di linee di assemblaggio. A tale scopo, il processore è costruito per eseguire una serie di operazioni. L'istruzione complessa è anche definita MULT, che opera banchi di memoria di un computer direttamente senza che il compilatore esegua le funzioni di memorizzazione e caricamento.

Architettura CISC

Caratteristiche dell'architettura CISC

- Per semplificare l'architettura del computer, CISC supporta la microprogrammazione.

- CISC ha un numero maggiore di istruzioni predefinite che rendono i linguaggi di alto livello facili da progettare e implementare.

- CISC è costituito da un numero inferiore di registri e da un numero maggiore di modalità di indirizzamento, generalmente da 5 a 20.

- Il processore CISC impiega un tempo di ciclo variabile per l'esecuzione delle istruzioni - cicli multi-clock.

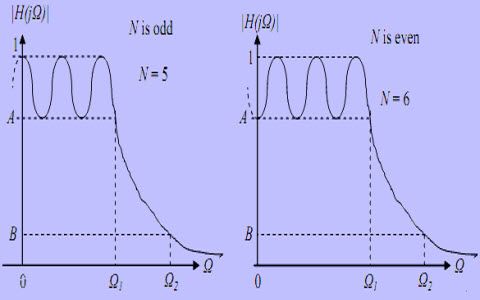

- A causa del complesso set di istruzioni del CISC, la tecnica del pipelining è molto difficile.

- Il CISC è costituito da un numero maggiore di istruzioni, generalmente da 100 a 250.

- Le istruzioni speciali vengono utilizzate molto raramente.

- Gli operandi in memoria vengono manipolati dalle istruzioni.

Vantaggi dell'architettura CISC

- Ogni istruzione in linguaggio macchina è raggruppata in un'istruzione di microcodice ed eseguita di conseguenza, quindi viene memorizzata nella memoria del processore principale, definita come implementazione del microcodice.

- Poiché la memoria del microcodice è più veloce della memoria principale, il set di istruzioni del microcodice può essere implementato senza una notevole riduzione della velocità rispetto all'implementazione cablata.

- L'intero nuovo set di istruzioni può essere gestito modificando il design del micro programma.

- CISC, il numero di istruzioni richieste per implementare un programma può essere ridotto creando ricchi set di istruzioni e può anche essere fatto per utilizzare la memoria principale lenta in modo più efficiente.

- A causa del superinsieme di istruzioni che consiste in tutte le istruzioni precedenti, questo semplifica la microcodifica.

Inconvenienti di CISC

- La quantità di tempo impiegato dalle diverse istruzioni sarà diversa - a causa di ciò - le prestazioni della macchina rallentano.

- La complessità del set di istruzioni e l'hardware del chip aumentano poiché ogni nuova versione del processore è costituita da un sottoinsieme delle generazioni precedenti.

- Solo il 20% delle istruzioni esistenti viene utilizzato in un tipico evento di programmazione, anche se esistono molte istruzioni specializzate che non vengono nemmeno utilizzate frequentemente.

- I codici condizionali sono impostati dalle istruzioni CISC come effetto collaterale di ciascuna istruzione che richiede tempo per questa impostazione e, poiché l'istruzione successiva modifica i bit del codice della condizione, il compilatore deve esaminare i bit del codice della condizione prima che ciò accada.

RISC vs. CISC

- I cicli di spreco possono essere prevenuti dal programmatore rimuovendo il codice non necessario nel RISC, ma mentre si utilizza il codice CISC porta a sprecare i cicli a causa dell'inefficienza del CISC.

- In RISC, ogni istruzione è concepita per eseguire una piccola attività in modo tale che, per eseguire un'attività complessa, più piccole istruzioni vengono utilizzate insieme, mentre solo poche istruzioni sono necessarie per eseguire la stessa attività utilizzando CISC, poiché è in grado di eseguire attività complesse poiché le istruzioni sono simili a un codice in alta lingua.

- CISC viene generalmente utilizzato per i computer mentre RISC viene utilizzato per smartphone, tablet e altri dispositivi elettronici.

La figura seguente mostra ulteriori differenze tra RISC e CISC

RISC vs. CISC

Pertanto, questo articolo discute sulle caratteristiche delle architetture RISC e CISC dei vantaggi e degli svantaggi dell'architettura dei processori RISC e CISC di RISC e CISC e le differenze tra le architetture RISC e CISC con una breve idea. Per ulteriori informazioni sulle architetture RISC e CISC, inviare le proprie domande commentando di seguito.

Crediti fotografici:

- Set di istruzioni del processore di arstechnica

- Architettura RISC di lsi-contest

- RISC vs. CISC di csarassignment